# Darbhanga College of Engineering, Darbhanga Computer Science & Engineering Computer Architecture, EEE 6th Semester (Question Paper)

#### 1. What is Computer Architecture ?

Ans: In computer engineering, computer architecture is a set of rules and methods that describe the functionality, organization, and implementation of computer systems. Some definitions of architecture define it as describing the capabilities and programming model of a computer but not a particular implementation.

Unit 1

2. What are the three categories of Computer Architecture ?

Ans: Almost all modern computers use the Von Neumann architecture model that was created by a mathematician in the 1940's. This model includes fundamental things like the computer's CPU, registry, memory, storage, logic unit and input/output (I/O) interface. Most computer's architecture can be divided into three categories. First, the hardware system includes the CPU, direct memory and data and graphics processors. Second, the Instruction Set Architecture directs the embedded programming language in the CPU. The ISA's programming defines the functions and capabilities of the CPU. Common definitions include word size, processor types, memory modes, data formats and user instructions. Third, the micro-architecture is the computer's international organization that defines data paths, storage, execution and processing. A computer's architecture may be created and maintained by systems engineers, application architects and software engineers.

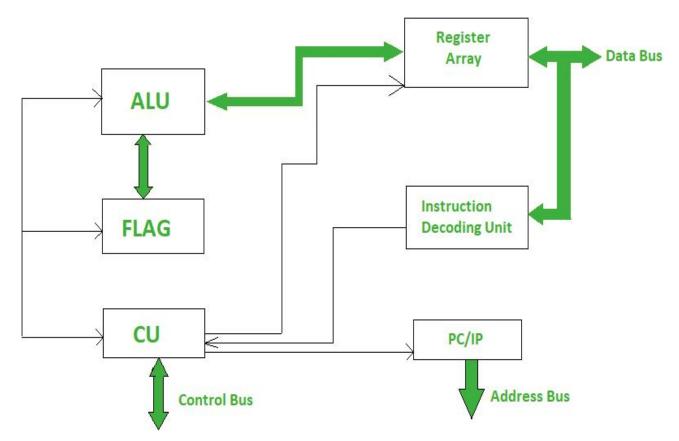

3. What are the common Components of a Microprocessor?

Ans: Some of the common components of a microprocessor are:

Control Unit. I/O Units. Arithmetic Logic Unit (ALU) Registers. Cache.

4. What are the various Interrupts in a Microprocessor system?

Ans: Interrupts are the signals generated by the external devices to request the microprocessor to perform a task. There are 5 interrupt signals, i.e. TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR.

Interrupt are classified into following groups based on their parameter -

- Vector interrupt In this type of interrupt, the interrupt address is known to the processor. For example: RST7.5, RST6.5, RST5.5, TRAP.

- Non-Vector interrupt In this type of interrupt, the interrupt address is not known to the processor so, the interrupt address needs to be sent externally by the device to perform interrupts. For example: INTR.

- **Maskable interrupt** In this type of interrupt, we can disable the interrupt by writing some instructions into the program. **For example:** RST7.5, RST6.5, RST5.5.

- Non-Maskable interrupt In this type of interrupt, we cannot disable the interrupt by writing some instructions into the program. For example: TRAP.

- **Software interrupt** In this type of interrupt, the programmer has to add the instructions into the program to execute the interrupt. There are 8 software interrupts in 8085, i.e. RST0, RST1, RST2, RST3, RST4, RST5, RST6, and RST7.

- **Hardware interrupt** There are 5 interrupt pins in 8085 used as hardware interrupts, i.e. TRAP, RST7.5, RST6.5, RST5.5, INTA.

**Note** – NTA is not an interrupt, it is used by the microprocessor for sending acknowledgement. TRAP has the highest priority, then RST7.5 and so on.

5. How Computer Architecture different from a Computer Organization?

| Computer Architecture                                                                                                 | Computer Organization                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Computer Architecture is concerned with the way hardware components are connected together to form a computer system. | Computer Organization is concerned with the structure<br>and behaviour of a computer system as seen by the<br>user. |

| It acts as the interface between hardware and software.                                                               | It deals with the components of a connection in a system.                                                           |

| Computer Architecture helps us to understand the functionalities of a system.                                         | Computer Organization tells us how exactly all the units<br>in the system are arranged and interconnected.          |

| A programmer can view architecture in terms of instructions, addressing modes and registers.                          | Whereas Organization expresses the realization of architecture.                                                     |

| While designing a computer system architecture is considered first.                                                   | An organization is done on the basis of architecture.                                                               |

| Computer Architecture deals with high-level design issues.                                                            | Computer Organization deals with low-level design issues.                                                           |

| Architecture involves Logic (Instruction sets, Addressing modes, Data types, Cache optimization)                      | Organization involves Physical Components (Circuit design, Adders, Signals, Peripherals)                            |

6. List out the types of bus.

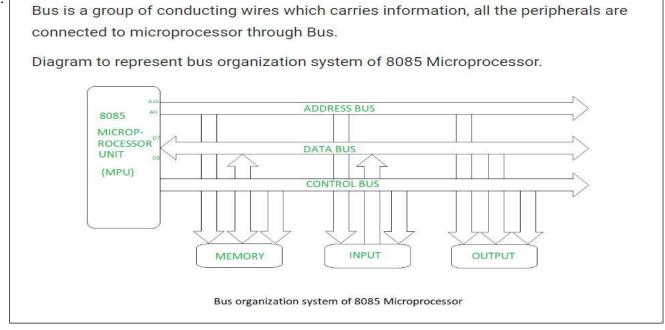

## Ans: Three types of bus are used.

• Address bus - carries memory addresses from the processor to other components such as primary storage and input/output devices. ...

- Data bus carries the data between the processor and other components. ...

- Control bus carries control signals from the processor to other components.

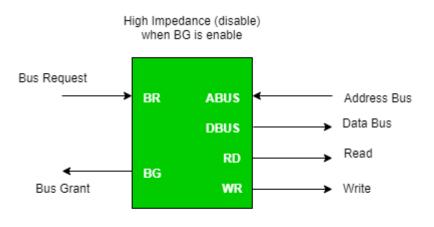

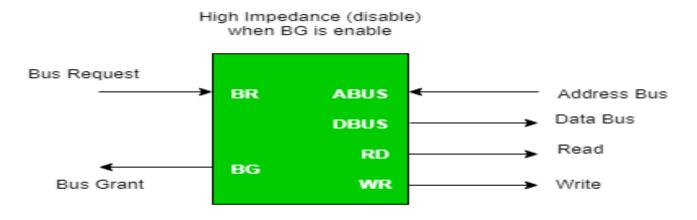

- 7. Define and figure out Bus organization.

#### Ans:

8. Define Program Counter.

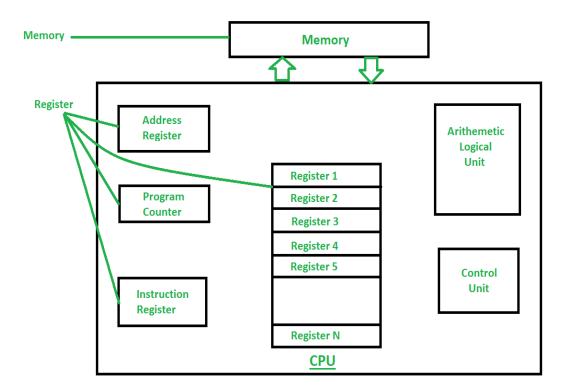

Ans: A **program counter** is a register in a computer processor that contains the address (location) of the instruction being executed at the current time.

9. Why we have the types of Registers?

Ans: There are **various types of Registers** those are used for **various** purpose. Some Mostly used **Registers** are Accumulator(AC), Data Register(DR), Address Register(AR), Program Counter(PC), Memory Data Register (MDR), Index Register(IR), Memory Buffer Register(MBR). **Registers** are used for performing the **various** operations.

10. What is Number Representation?

Ans: When working with any kind of digital electronics in which numbers are being represented, it is important to understand the different ways numbers are represented in these systems. Almost without fail, numbers are represented by two voltage levels which can represent a one or a zero (an interesting exception to this rule is the new memory device recently announced by Intel which uses one of four possible voltage levels, thereby increasing the amount of information that can be stored in a given space). The number system based on ones and zeroes is called the binary system (because there are only two possible digits). Before discussing the binary system, a review of the decimal (ten possible digits) system is in order, because many of the concepts of the binary system will be easier to understand when introduced alongside their decimal counterpart.

You should all have some familiarity with the decimal system. For instance, to represent the positive integer one hundred and twenty-five as a decimal number, we can write (with the postivie sign implied). The subscript 10 denotes the number as a base 10 (decimal) number.

12510 = 1\*100 + 2\*10 + 5\*1 = 1\*102 + 2\*101 + 5\*100

11. What is 2's complement method and give few examples?

Ans: **Two's complement** is a mathematical operation on binary numbers, and is an **example** of a radix **complement**. It is used in computing as a **method** of signed number representation. The **two's complement** of an N-bit number is defined as its **complement** with respect to  $2^{N}$ .

For example, 2's complement of "01000" is "11000" (Note that we first find one's complement of 01000 as 10111). If there are all 1's (in one's complement), we add an extra 1 in the string. For example, 2's complement of "000" is "1000" (1's complement of "000" is "111").

12. Define Floating point representation of numbers.

Ans: The term **floating point** refers to the fact that a **number's** radix **point** (decimal **point**, or, more commonly in computers, binary **point**) can "**float**"; that is, it can be placed anywhere relative to the significant digits of the **number**.

In computers, floating-point numbers are represented in scientific notation of fraction (F) and exponent (E) with a radix of 2, in the form of  $F \times 2^{E}$ . Both E and F can be positive as well as negative. Modern computers adopt IEEE 754 standard for representing floating-point numbers.

#### 13. Difference between Signed magnitude and 2's complement?

| SIGNED MAGNITUDE METHOD              | 2'S COMPLEMENT METHOD       |

|--------------------------------------|-----------------------------|

| It is a method to denote fixed point | It is also used to denote   |

| signed numbers.                      | fixed point signed numbers. |

|                                      | Number is considered as a   |

| Number is divided into two parts.    | whole.                      |

|                                      | Sign bit is not considered  |

| Sign bit is considered explicitly.   | explicitly.                 |

| Additional hardware is required for  | No additional hardware is   |

| resultant sign of arithmetic.        | required in 2's complement  |

Ans:

| SIGNED MAGNITUDE METHOD                 | 2'S COMPLEMENT METHOD         |

|-----------------------------------------|-------------------------------|

|                                         | method.                       |

|                                         | Addition and subtraction are  |

| Addition and subtraction are            | performed by using adder      |

| performed on separate hardware.         | only.                         |

| It has two different representation for | 0 has only one                |

| 0. One is +0 and second is -0. (+0 :    | representation for -0 and +0  |

| 0000 0000) & (-0 : 1000 0000)           | (+0 or -0 : 0000 0000).       |

|                                         | It assigns negative weight to |

| It is non-weighted system.              | the sign bit.                 |

14. How the negative numbers are stored in memory?

Ans: Suppose the following fragment of code, int a = -34; Now how will this be stored in memory. So here is the complete theory. Whenever a number with minus sign is encountered, the number (ignoring minus sign) is converted to its binary equivalent. Then the two's complement of the number is calculated. That two's complement is kept at place allocated in memory and the sign bit will be set to 1 because the binary being kept is of a negative number. Whenever it comes on accessing that value firstly the sign bit will be checked if the sign bit is 1 then the binary will be two's complemented and converted to equivalent decimal number and will be represented with a minus sign.

Let us take an example: Example – int a = -2056; Binary of 2056 will be calculated which is:

So finally the above binary will be stored at memory allocated for variable a. When it comes on accessing the value of variable a, the above binary will be retrieved from the memory location, then its sign bit that is the left most bit will be checked as it is 1 so the binary number is of a The above binary number will be converted to its decimal equivalent which is 2056 and as the sign bit was 1 so the decimal number which is being gained from the binary number will be represented with a minus sign. In our case -2056.

15. Why are negative numbers stored as 2's complement?

Ans: When doing addition/subtraction on binary numbers in other representations we need to apply different logics (circuits) to perform addition and subtraction. In 2s-complement representation, we represent a positive number as it is and negative number by its corresponding 2s-complement, so we can use the same circuit to perform addition and subtraction.

For example: to add 6+3 using 5 bit 2s-complement representation,

00110 + 00011 -----01001 To subtract 6-3, rewrite as 6+ (-3): 00110 + 11101 (2s-complement of 3) -----00011

**16**. What is Booth's Algorithm?

Ans: Booth algorithm gives a procedure for multiplying binary integers in signed 2's complement representation in efficient way, i.e., less number of additions/subtractions required. It operates on the fact that strings of 0's in the multiplier require no addition but just shifting and a string of 1's in the multiplier from bit weight  $2^k$  to weight  $2^m$  can be treated as  $2^k(k+1)$  to  $2^m$ .

As in all multiplication schemes, booth algorithm requires examination of the multiplier bits and shifting of the partial product. Prior to the shifting, the multiplicand may be added to the partial product, subtracted from the partial product, or left unchanged according to following rules:

- 1. The multiplicand is subtracted from the partial product upon encountering the first least significant 1 in a string of 1's in the multiplier

- 2. The multiplicand is added to the partial product upon encountering the first 0 (provided that there was a previous '1') in a string of 0's in the multiplier.

- 3. The partial product does not change when the multiplier bit is identical to the previous multiplier bit.

- 17. What are the different Instruction Cycles?

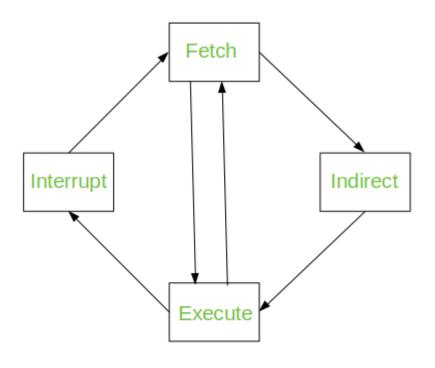

#### Ans: The Instruction Cycle –

Each phase of Instruction Cycle can be decomposed into a sequence of elementary micro-operations. In the above examples, there is one sequence each for the *Fetch, Indirect, Execute and Interrupt Cycles*.

The Instruction Cycle

The *Indirect Cycle* is always followed by the *Execute Cycle*. The *Interrupt Cycle* is always followed by the *Fetch Cycle*. For both fetch and execute cycles, the next cycle depends on the state of the system.

# **Objective**

18. The smallest integer that can be represented by an 8-bit number in 2's complement form is

a) -256 b) -128 c) -127 d) 0

Answer: (b)

- 19. The decimal value 0.5 in IEEE single precision floating point representation has

- a) fraction bits of 000...000 and exponent value of 0

- b) fraction bits of 000...000 and exponent value of -1

- c) fraction bits of 100...000 and exponent value of 0

- d) no exact representation

Answer: (b)

| 20.<br>re | P is a 16-bit signed integer.<br>presentation of 8*P          | The 2's compl                                          | ement represen | tation of P is ( | (F87B)16.The 2's complement    |

|-----------|---------------------------------------------------------------|--------------------------------------------------------|----------------|------------------|--------------------------------|

|           | a) (C3D8)16<br>Answer: (a)                                    | b) (187B)16                                            | c) (18         | 7B)10            | d) (187B)8                     |

| 21.       | (1217)8 is equivalent to<br>a) (1217)16<br><b>Answer: (b)</b> | b) (028F)16                                            | c)(2297)10     | d) (0B17)16      |                                |

| 22.       | Consider the equation (123)                                   | 5 = (x8)y with                                         | x and y as un  | known. The nu    | umber of possible solutions is |

|           | a) 0<br>Answer: (d)                                           | b) 1                                                   | c) 2           | d) 3             |                                |

| 23.       |                                                               | can be represent<br>- $(2^{(n-1)})$ to + $(2^{(n-1)})$ | -              | 2's compleme     | ent number system is           |

| 24.       | The hexadecimal representa<br>a) 1AF b)                       | tion of 6578 is<br>D78 c) D7                           | 1 d) 32H       | -                |                                |

|           | Ans: 1AF.                                                     |                                                        |                |                  |                                |

25. Define Micro-Operation.

Ans: **Micro-operation**. In computer central processing units, **micro-operations** (also known as a **micro**-ops or  $\mu$ ops) are detailed low-level instructions used in some designs to implement complex machine instructions (sometimes termed macro-instructions in this context).

Unit-2

26. Define Instruction Set Architecture.

Ans: The instruction set, also called ISA (instruction set architecture), is part of a computer that pertains to programming, which is basically machine language. The instruction set provides commands to the processor, to tell it what it needs to do.

27. Define instruction.

Ans: Three Categories of Instructions: The instruction set is a collection of instructions each representing a CPU operation. In assembly language, the instructions are represented by the mnimonics and the operands (or their addresses) involved in the operation Data manipulation.

28. What is the types of instructions?

### **Ans: Three Categories of Instructions:**

The instruction set is a collection of instructions each representing a CPU operation. In assembly language, the instructions are represented by the *mnimonics* and the operands (or their addresses) involved in the operation.

- 1. Data manipulation

- Arithmetic manipulation:

add, sub, mult, div, etc.

• Logic and bit manipulation:

and, or, nor, xor, etc.

• Shift and rotation (to right or left):

sll, srl, sra, rol, ror, etc.

**Note:** Instruction srl (shift right logical) shifts a 0 into the vacated bit (the sign bit), while instruction sra (shift right arithmetic) repeats the sign bit (sign extension for signed 2's complement).

## 2. Data transfer

• transfer data between MM and CPU:

lw (load word), la (load address), lb (load byte),

sw (store word), sb (store byte), etc.

• transfer data between registers in RF:

move, mfhi, mflo, mthi, mtlo,

## 3. Program control

branch to instruction other than the one following the current one conditionally or unconditionally (based on comparison between two operands or between one operand and zero):

b, beq, bne, bgt, blt, bge, ble, beqz, bnez, bgez, bgtz,

• jump to different segments of the program (functions, subroutines, etc.)

j, jal, jalr, jr, etc.

## 29. Who define the maximum length of each type of instruction?

Ans: n instruction format defines the different component of an instruction. The main components of an instruction are opcode (which instruction to be executed) and operands (data on which instruction to be executed). Here are the different terms related to instruction format:

- 1. Instruction set size It tells the total number of instructions defined in the processor.

- 2. Opcode size It is the number of bits occupied by the opcode which is calculated by taking log of instruction set size.

- 3. Operand size It is the number of bits occupied by the operand.

- 4. Instruction size It is calculated as sum of bits occupied by opcode and operands.

30. What are Instruction Formats (Zero, One, Two and Three Address Instruction)?

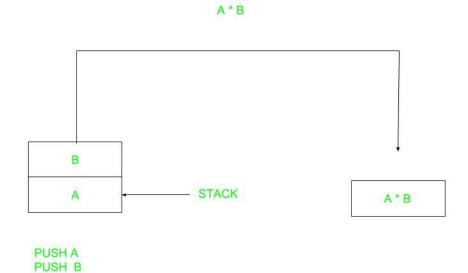

## 1. Ans: Zero Address Instructions -

A stack based computer do not use address field in instruction. To evaluate a expression first it is converted to revere Polish Notation i.e. Post fix Notation.

Expression: X = (A+B)\*(C+D) Postfixed : X = AB+CD+\* TOP means top of stack M[X] is any memory location PUSH A TOP = A

| PUSH | В | TOP = B              |

|------|---|----------------------|

| ADD  |   | TOP = A + B          |

| PUSH | С | TOP = C              |

| PUSH | D | TOP = D              |

| ADD  |   | TOP = C+D            |

| MUL  |   | $TOP = (C+D)^*(A+B)$ |

| POP  | Х | M[X] = TOP           |

#### 2. One Address Instructions –

This use a implied ACCUMULATOR register for data manipulation. One operand is in accumulator and other is in register or memory location. Implied means that the CPU already know that one operand is in accumulator so there is no need to specify it.

| opcode | operand/address of operand | mode |

|--------|----------------------------|------|

|--------|----------------------------|------|

Expression: X = (A+B)\*(C+D)

AC is accumulator

M[] is any memory location

| M[T] | is | temporary | location |

|------|----|-----------|----------|

|------|----|-----------|----------|

| LOAD  | А | AC = M[A]      |

|-------|---|----------------|

| ADD   | В | AC = AC + M[B] |

| STORE | Т | M[T] = AC      |

| LOAD  | С | AC = M[C]      |

| ADD   | D | AC = AC + M[D] |

| MUL   | Т | AC = AC * M[T] |

| STORE | Х | M[X] = AC |

|-------|---|-----------|

|-------|---|-----------|

#### 3. Two Address Instructions -

This is common in commercial computers. Here two address can be specified in the instruction. Unlike earlier in one address instruction the result was stored in accumulator here result cab be stored at different location rather than just accumulator, but require more number of bit to represent address.

| opcode Destination address | Source address | mode |

|----------------------------|----------------|------|

|----------------------------|----------------|------|

Here destination address can also contain operand.

Expression: X = (A+B)\*(C+D)

R1, R2 are registers

M[] is any memory location

| MOV | R1, A  | R1 = M[A]      |

|-----|--------|----------------|

| ADD | R1, B  | R1 = R1 + M[B] |

| MOV | R2, C  | R2 = C         |

| ADD | R2, D  | R2 = R2 + D    |

| MUL | R1, R2 | R1 = R1 * R2   |

| MOV | X, R1  | M[X] = R1      |

#### 4. Three Address Instructions –

This has three address field to specify a register or a memory location. Program created are much short in size but number of bits per instruction increase. These instructions make creation of program much easier but it does not mean that program will run much faster because now instruction only contain more information but each micro operation (changing content of register, loading address in address bus etc.) will be performed in one cycle only.

| opcode Destination address | Source address | Source address | mode |

|----------------------------|----------------|----------------|------|

|----------------------------|----------------|----------------|------|

#### Expression: X = (A+B)\*(C+D)

| R1, R2 a | re registers   |                  |  |

|----------|----------------|------------------|--|

| M[] is a | ny memory loca | tion             |  |

| ADD      | R1, A, B       | R1 = M[A] + M[B] |  |

| ADD      | R2, C, D       | R2 = M[C] + M[D] |  |

| MUL      | X, R1, R2      | M[X] = R1 * R2   |  |

. Difference between 3-address instruction and 0-address instruction.

| Ans: Difference between Three-Address Instruction and Zero-Address Instruction : |  |

|----------------------------------------------------------------------------------|--|

|----------------------------------------------------------------------------------|--|

| THREE-ADDRESS<br>INSTRUCTION                                      | ZERO-ADDRESS<br>INSTRUCTION                                   |

|-------------------------------------------------------------------|---------------------------------------------------------------|

| It has four fields.                                               | It has only one field.                                        |

| It has one field for opcode and three fields for address.         | It has one field for opcode and no fields for address.        |

| It has long instruction length.                                   | It has shorter instruction.                                   |

| It is slower accessing location inside processor than memory.     | It is faster accessing location inside processor than memory. |

| There is distinct address fields for destination and source.      | There is no address field common for destination and source.  |

| In 3-address format, destination address can not contain operand. | While in 0-address format, there is no field for operand.     |

| In 3-address format, number of                                    | While in 0-address format,                                    |

| THREE-ADDRESS<br>INSTRUCTION                           | ZERO-ADDRESS<br>INSTRUCTION             |

|--------------------------------------------------------|-----------------------------------------|

| instructions are less.                                 | number of instructions are more.        |

| It may need three memory accesses for one instruction. | It does not need three memory accesses. |

**32**. Difference between 3-address instruction and 1-address instruction.

| Ans:                                                                                |                                                                              |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| THREE-ADDRESS INSTRUCTION                                                           | <b>ONE-ADDRESS INSTRUCTION</b>                                               |

| It has four fields.                                                                 | It has only two fields.                                                      |

| It has one field for opcode and three fields for address.                           | It also has one field for opcode but there is only<br>one field for address. |

| It has long instruction length.                                                     | It has shorter instruction.                                                  |

| There may be three memory accesses needed for an instruction.                       | There is a single memory access needed for an instruction.                   |

| It is slower accessing location inside processor than memory.                       | It is faster accessing location inside processor than memory.                |

| It disadvantage i.e. three memory<br>access is eliminated by two-address<br>memory. | It eliminated two memory access.                                             |

| There are three location for operand and result.                                    | There is only one location for operand and result.                           |

33. What is the difference between Hardwired and Micro-programmed Control Unit ?

## Ans: Difference between Hardwired and Microprogrammed Control Unit:

| ATTRIBUTES         | HARDWIRED CONTROL UNIT   | MICROPROGRAMMED<br>CONTROL UNIT |

|--------------------|--------------------------|---------------------------------|

| 1. Speed           | Speed is fast            | Speed is slow                   |

| 2. Cost of         |                          |                                 |

| Imlementation      | More costlier.           | Cheaper.                        |

|                    | Not flexible to          |                                 |

|                    | accommodate new          | More flexible to                |

|                    | system specification or  | accommodate new                 |

|                    | new instruction redesign | system specification or         |

| 3. Flexibility     | is required.             | new instruction sets.           |

| 4. Ability to      |                          |                                 |

| Handle Complex     | Difficult to handle      | Easier to handle complex        |

| Instructions       | complex intruction sets. | intruction sets.                |

|                    | Complex decoding and     | Easier decoding and             |

| 5. Decoding        | sequencing logic.        | sequencing logic.               |

| 6. Applications    | RISC Microprocessor      | CISC Microprocessor             |

| 7. Instruction set |                          |                                 |

| of Size            | Small                    | Large                           |

| 8. Control         |                          |                                 |

| Memory             | Absent                   | Present                         |

| 9. Chip Area       |                          |                                 |

| Required           | Less                     | More                            |

| ATTRIBUTES     | HARDWIRED CONTROL UNIT | MICROPROGRAMMED<br>CONTROL UNIT |

|----------------|------------------------|---------------------------------|

|                | Occurrence of error is | Occurrence of error is          |

| 10. Occurrence | more                   | less                            |

# **Objective**

34. Technically speaking, what is the most accurate description of a peripheral device?

- a) A device that is connected to a computer but is not part of the core computer architecture

- b) A device that plugs into a computer using a USB connection

- c) A device that provides input and output functions for a computer system

- d) A device connected to a computer using a cable.

Ans: a)

35. What are the three general types of peripheral devices?

- a) Input, output and storage

- b) Mouse, keyboard and monitor

- c) Audio, video and print output.

- d) Internal, wired external and wireless external.

Ans: a)

36. Which of the following is NOT a computer peripheral?

- a) Central processing unit

- b) Scanner

- b) Printer

- d) Microphone

Ans: a)

37. The interrupt-request line is a part of the \_\_\_\_\_\_a) Data line b) Control line c) Address line d) None of the mentioned Ans: b)

39. The signal sent to the device from the processor to the device after receiving an interrupt is

a) Interrupt-acknowledge b) Return signal c) Service signal d) Permission signal Ans: a)

| 40. When the   | e process is returned | d after an interru | upt service      | should be l       | oaded again.      |

|----------------|-----------------------|--------------------|------------------|-------------------|-------------------|

| i              | ) Register contents   |                    |                  |                   |                   |

| i              | i) Condition codes    |                    |                  |                   |                   |

| ii             | ii) Stack contents    |                    |                  |                   |                   |

| i              | v) Return addresses   | 5                  |                  |                   |                   |

| a) i, iv       | b) ii, iii and iv     | c) iii, i          | v d) i, ii       |                   |                   |

| Ans: d)        |                       |                    |                  |                   |                   |

| 41 The time    | between the receiv    | er of an interru   | ot and its servi | ce is             |                   |

|                | Interrupt delay       | -                  | -                |                   | d) Switching time |

| Ans: b)        | interrupt delay       | o) interrupt in    | tene y           | c) Cycle tille    | d) Switching time |

| 42. Interrupts | s form an important   | t part ofs         | systems.         |                   |                   |

| a)             | Batch processing      | b) Multitaskir     | ng c) Rea        | ll-time processir | ng d) Multi-user  |

| Ans: c)        |                       |                    |                  |                   |                   |

| 43. An interr  | upt that can be tem   | porarily ignored   | l is             |                   |                   |

|                | -                     | nterrupt           |                  |                   |                   |

|                | ,                     | nterrupt           | <i>,</i>         | -                 |                   |

|                |                       |                    |                  |                   |                   |

| Ans: c)        |                       |                    |                  |                   |                   |

|                |                       |                    |                  |                   |                   |

|                |                       |                    |                  |                   |                   |

44. Difference between Random Access Memory (RAM) and Content Addressable Memory (CAM)

Ans: RAM:

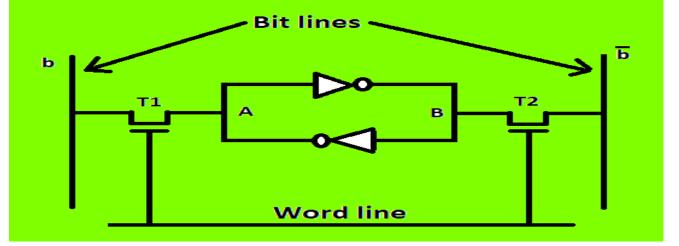

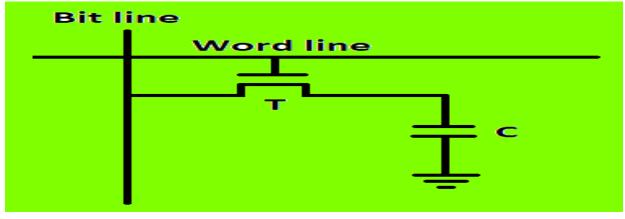

Random Access Memory (RAM) is used to read and write. It is the part of primary memory and used in order to store running applications (programs) and program's data for performing operation. It is mainly of two types: Dynamic RAM (or DRAM) and Static RAM (or SRAM).

Unit-3

CAM:

Content Addressable Memory (CAM) is also known as Associative Memory, in which the user supplies data word and associative memory searches its entire memory and if the data word is found, It returns the list of addresses where that data word was located.

45. Difference between Virtual memory and Cache memory.

Ans:

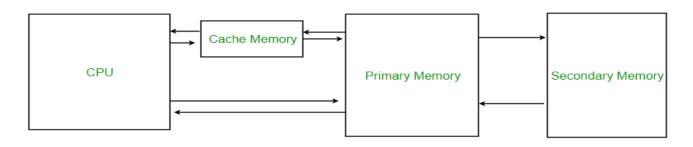

**Cache memory** increases the accessing speed of CPU. It is not a technique but a memory unit i.e a storage device. In cache memory, recently used data is copied. Whenever the program is ready to be executed, it is fetched from main memory and then copied to the cache memory. But, if its copy is already present in the cache memory then the program is directly executed.

**Virtual Memory** increases the capacity of main memory. Virtual memory is not a storage unit, its a technique. In virtual memory, even such programs which have a larger size than the main memory are allowed to be executed.

Difference between Virtual memory and Cache memory:

| S.NO | VIRTUAL MEMORY                                                                                         | CACHE MEMORY                                                    |

|------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 1.   | Virtual memory increases the capacity of main memory.                                                  | While cache memory increase the accessing speed of CPU.         |

| 2.   | Virtual memory is not a memory unit, its a technique.                                                  | Cache memory is exactly a memory unit.                          |

| 3.   | The size of virtual memory is greater than the cache memory.                                           | While the size of cache memory is less than the virtual memory. |

| 4.   | Operating System manages the Virtual memory.                                                           | On the other hand hardware manages the cache memory.            |

| 5.   | In virtual memory, The program with size<br>larger than the main memory are<br>executed.               | While in cache memory, recently used data is copied into.       |

| 6.   | In virtual memory, mapping frameworks<br>is needed for mapping virtual address to<br>physical address. | While in cache memory, no such mapping frameworks is needed.    |

46. Define memory and memory units.

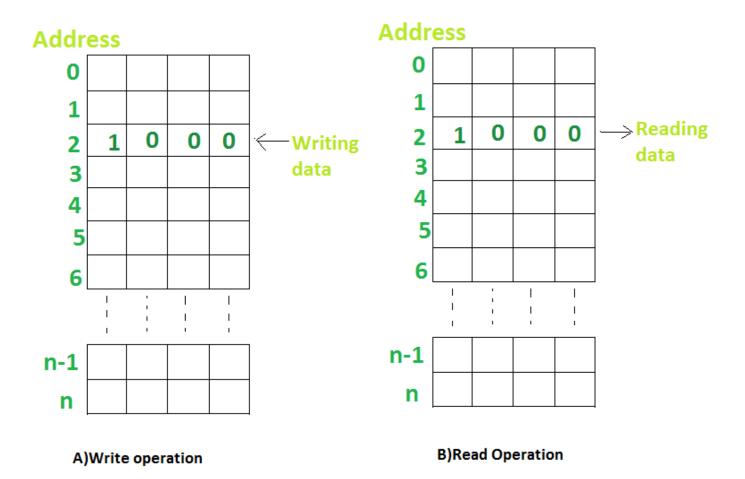

Ans: Memories are made up of registers. Each register in the memory is one storage location. Storage location is also called as memory location. Memory locations are identified using **Address**. The total number of bit a memory can store is its **capacity**.

A storage element is called a **Cell**. Each register is made up of storage element in which one bit of data is stored. The data in a memory are stored and retrieved by the process called **writing** and **reading** respectively.

A word is a group of bits where a memory unit stores binary information. A word with group of 8 bits is calleda **byte**.

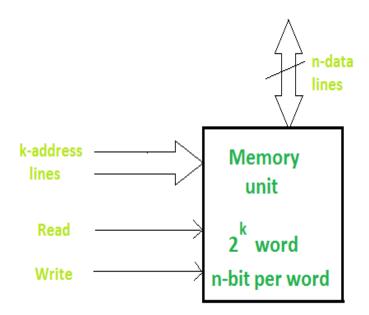

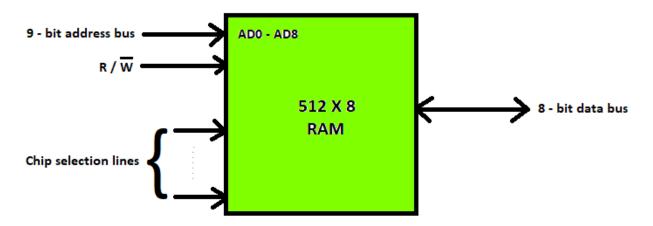

A memory unit consists of data lines, address selection lines, and control lines that specify the direction of transfer. The block diagram of a memory unit is shown below:

Data lines provide the information to be stored in memory. The control inputs specify the direction transfer. The k-address lines specify the word chosen.

When there are k address lines,  $2^k$  memory word can be accessed.

47. Define Secondary Memory.

Ans: **Secondary memory** is where programs and data are kept on a long-term basis. Common **secondary** storage devices are the hard disk and optical disks. The hard disk has enormous storage capacity compared to main **memory**. The hard disk is usually contained inside the case of a computer.

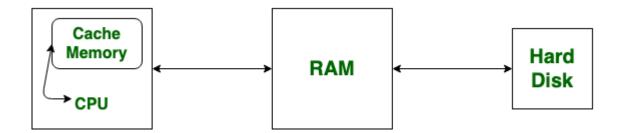

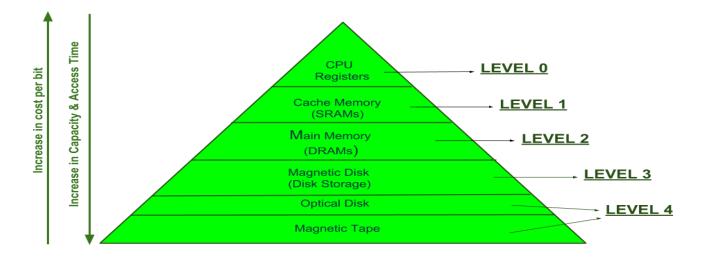

48. Define a concept of Memory hierarchy design.

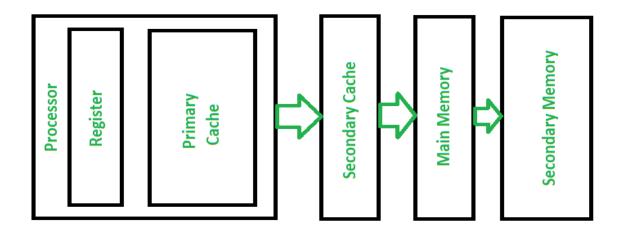

Ans: In the Computer System Design, Memory Hierarchy is an enhancement to organize the memory such that it can minimize the access time. The Memory Hierarchy was developed based on a program behavior known as locality of references. The figure below clearly demonstrates the different levels of memory hierarchy :

## MEMORY HIERARCHY DESIGN

This Memory Hierarchy Design is divided into 2 main types:

1. External Memory or Secondary Memory -

Comprising of Magnetic Disk, Optical Disk, Magnetic Tape i.e. peripheral storage devices which are accessible by the processor via I/O Module.

## 2. Internal Memory or Primary Memory –

Comprising of Main Memory, Cache Memory & CPU registers. This is directly accessible by the processor.

We can infer the following characteristics of Memory Hierarchy Design from above figure:

1. Capacity:

It is the global volume of information the memory can store. As we move from top to bottom in the Hierarchy, the capacity increases.

2. Access Time:

It is the time interval between the read/write request and the availability of the data. As we move from top to bottom in the Hierarchy, the access time increases.

## 3. Performance:

Earlier when the computer system was designed without Memory Hierarchy design, the speed gap increases between the CPU registers and Main Memory due to large difference in access time. This results in lower performance of the system and thus, enhancement was required. This enhancement was made in the form of Memory Hierarchy Design because of which the performance of the system increases. One of the most significant ways to increase system performance is minimizing how far down the memory hierarchy one has to go to manipulate data.

## 4. Cost per bit:

As we move from bottom to top in the Hierarchy, the cost per bit increases i.e. Internal Memory is costlier than External Memory.

#### 48. Define Memory Organisation.

Ans: **Memory Organization** in Computer Architecture. A **memory** unit is the collection of storage units or devices together. The **memory** unit stores the binary information in the form of bits. Generally, **memory**/storage is classified into 2 categories: Volatile **Memory**: This loses its data, when power is switched off.

49. What are the difference between Byte Addressable Memory and Word Addressable Memory?

Ans:

| <b>BYTE ADDRESSABLE MEMORY</b>                                                                                                                                              | WORD ADDRESSABLE MEMORY                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When the <i>data space in the cell = 8</i><br><i>bits</i> then the corresponding <i>address</i><br><i>space</i> is called as <u>Byte Address</u> .                          | When the <i>data space in the cell = word length of</i> $CPU$ then the corresponding <i>address space</i> is called as <u>Word Address</u> .                                                                      |

| Based on this data storage i.e. <i>Bytewise storage</i> , the memory chip configuration is named as <b>Byte Addressable Memory</b> .                                        | Based on this data storage i.e. <i>Wordwise storage</i> , the memory chip configuration is named as <u>Word</u> <u>Addressable Memory</u> .                                                                       |

| For eg. : <b>64K X 8</b> chip has 16 bit Address<br>and <b>cell size = 8 bits (1 Byte)</b> which means<br>that in this chip, data is stored <u>byte by</u><br><u>byte</u> . | For eg. : For a 16-bit CPU, <b>64K X 16</b> chip has 16 bit<br>Address & <b>cell size = 16 bits (Word Length of</b><br><b>CPU</b> ) which means that in this chip, data is stored <u>word</u><br><u>by word</u> . |

#### NOTE

i) The most important point to be noted is that in case of either of Byte Address or Word Address, *the address size* can be any number of bits (depends on the number of cells in the chip) but the *cell size* differs in each case.

ii)The default memory configuration in the Computer design is Byte Addressable .

50. Difference between Register and Memory

Ans:

1. Register :

Registers are the smallest data holding elements that are built into the processor itself. These are the memory locations that are directly accessible by the processor. It may hold an instruction, a storage address or any kind of data such as a bit sequence or individual characters. For example, an instruction may specify that the contents of two defined registers be multiplied together and then placed in a specific register.

Example: Accumulator register, Program counter, Instruction register, Address register, etc.

## 2. Memory :

Memory is a hardware device used to store computer programs, instructions and data. The memory that is internal to the processor is a primary memory (RAM), and the memory that is external to the processor is a <u>secondary memory (Hard Drive)</u>. Memory can also be categorized on the basis of volatile and non-volatile memory. Volatile memory is memory that loses its contents when the computer or hardware device loses power. <u>RAM (Random Access Memory)</u> is an example of volatile memory. Non-volatile memory is the memory that keeps its contents even if power gets lost. <u>EPROM</u> is an example of non-volatile memory.

Example : RAM, EPROM etc.

#### **Difference between Register and Memory :**

| S.NO. | REGISTER                                                                                                    | MEMORY                                                                                                       |

|-------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 1.    | Registers hold the operands or instruction that CPU is currently processing.                                | Memory holds the<br>instructions and the data<br>that the currently<br>executing program in<br>CPU requires. |

| 2.    | Register holds the small amount of data around 32-bits to 64-bits.                                          | Memory of the computer<br>can range from some GB<br>to TB.                                                   |

| 3.    | CPU can operate on<br>register contents at the<br>rate of more than one<br>operation in one clock<br>cycle. | CPU accesses memory at<br>the slower rate than<br>register.                                                  |

| 4.    | Types are Accumulator<br>register, Program counter,<br>Instruction register,<br>Address register, etc.      | Type of memory are RAM,etc.                                                                                  |

| 5.    | Registers can be control<br>i.e. you can store and<br>retrieve information from<br>them.                    | Memory is almost not controllable.                                                                           |

| 6.    | Registers are faster than memory.                                                                           | RAM is much slower than registers.                                                                           |

51. Difference between Memory and Storage.

## Ans: **Memory**

The term memory refers to the component within your computer that allows you to access data that is stored for a short term. You may recognize this component as DRAM, or dynamic random-access memory. Your computer performs many operations by accessing data stored in its short-term memory. Some examples of such operations include editing a document, loading applications and browsing the Internet. The speed and performance of your system depends on the amount of memory that is installed on your computer. If you have a desk and a filing cabinet, the desk represents the memory of your computer. Items you will need to use soon are kept in your desk for easy access. However, not much can be stored in a desk due to its size limitations.

# Storage

Whereas memory refers to the location of short-term data, storage is the component of your computer that allows you to store and access data on a long-term basis. Usually, storage comes in the form of a solid-state drive or a hard drive. Storage allows you to access and store your applications, operating system and files for an indefinite period of time.

While the desk represents the computer's memory, the filing cabinet represents the storage of your computer. Items that must be kept yet won't necessarily be accessed soon are stored in the filing cabinet. Due to the size of the filing cabinet, many things can be stored.

An important distinction between memory and storage is that the former clears when the computer is turned off. On the other hand, storage remains intact no matter how many times you shut off your computer. Therefore, in the desk and filing cabinet analogy, any files that are left on your desk when you leave the office will be thrown away. Everything in your filing cabinet will remain.

52. What is CPU register?

Ans: The term CPU Register is often used to refer only to the group of registers that can be directly indexed for input or output of an instruction, as defined by the instruction set. More properly, these are called the "*architected registers*". For instance, the x86 instruction set defines a set of eight 32-bit registers, but a CPU that implements the X86 instruction set will contain many more hardware registers than just these eight.

## There are several other classes of registers:

(a) **Accumulator**: It is most frequently used register used to store data taken from memory. Its number varies from microprocessor to microprocessor.

(b) **General Purpose registers**: General purpose registers are used to store data and intermediate results during program execution. Its contents can be accessed through assembly programming.

(c) **Special purpose Registers**: Users do not access these registers. These are used by computer system at the time of program execution. Some types of special purpose registers are given below:

- Memory Address Register (MAR): It stores address of data or instructions to be fetched from memory.

- **Memory Buffer Register (MBR)**: It stores instruction and data received from the memory and sent from the memory.

- **Instruction Register (IR):** Instructions are stored in instruction register. When one instruction is completed, next instruction is fetched in memory for processing.

- **Program Counter (PC):** It counts instructions.

The <u>instruction cycle</u> is completed into two phases: (a) **Fetch Cycle** and (b) **Execute Cycle**. There are two parts in instruction- opcode and operand. In fetch cycle **opcode** of instruction is fetched into CPU. The opcode, at first, is reached to Data Register (DR), then to Instruction Register (IR). Decoder accesses the opcode and it decodes opcode and type of operation is declared to CPU and execution cycle is started.

#### 53. What is Cache memory?

Ans: Cache memory is an extremely fast memory type that acts as a buffer between RAM and the CPU. It holds frequently requested data and instructions so that they are immediately available to the CPU when needed. Cache memory is used to reduce the average time to access data from the Main memory.

#### 54. Difference between Primary and Secondary Memory.

| $\Delta ns$ . The difference betw | een Primary memor  | y and Secondary memory: |

|-----------------------------------|--------------------|-------------------------|

| Alls. The unreferice betw         | cell r mai y memor | y and Secondary memory. |

| SR.NO. | PRIMARY MEMORY                                                                                 | SECONDARY MEMORY                                                                           |

|--------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 1.     | Primary memory is temporary.                                                                   | Secondary memory is permanent.                                                             |

| 2.     | Primary memory is<br>directly accessible by<br>Processor/CPU.                                  | Secondary memory is not directly accessible by the CPU.                                    |

| 3.     | Nature of Parts of<br>Primary memory varies,<br>RAM- volatile in nature.<br>ROM- Non-volatile. | It's always Non-volatile in nature.                                                        |

| 4.     | Primary memory devices<br>are more expensive than<br>secondary storage<br>devices.             | Secondary memory devices are<br>less expensive when compared to<br>primary memory devices. |

| 5.     | The memory devices used<br>for primary memory are<br>semiconductor memories.                   | The secondary memory devices are magnetic and optical memories.                            |

| 6.     | Primary memory is also<br>known as Main memory<br>or Internal memory.                          | Secondary memory is also known<br>as External memory or Auxiliary<br>memory.               |

| 7.     | Examples: RAM, ROM,<br>Cache memory, PROM,<br>EPROM, Registers, etc.                           | Examples: Hard Disk, Floppy Disk, Magnetic Tapes, etc.                                     |

55. Difference between Memory based and Register based Addressing Modes.

Ans: Addressing modes are the operations field specifies the operations which need to be performed. The operation must be executed on some data which is already stored in computer registers or in the memory. The way of choosing operands during program execution is dependent on addressing modes of the

instruction. "The addressing mode specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually referenced. "Basically how we are interpreting the operand which is given in the instruction is known as addressing mode.

Addressing mode very much depend on the type of CPU organisation. There are three types of CPU organisation:

- 1. Single Accumulator organisation

- 2. General register organisation

- 3. Stack organisation

Addressing modes is used for one or both of the purpose. These can also be said as the **advantages** of using addressing mode:

- 1. To give programming versatility to the user by providing such facilities as pointers to memory, counter for loop control, indexing of data, and program relocation.

- 2. To reduce the number of bits in the addressing field of the instruction.

There are numbers of addressing modes available and it depends on the architecture and CPU organisation which of the addressing modes can be applied.

| MEMORY BASED                        | REGISTER BASED ADDRESSING              |

|-------------------------------------|----------------------------------------|

| ADDRESSING MODES                    | MODES                                  |

| The operand is present in           | An operand will be given in one of     |

| memory and its address is given     | the register and register number will  |

| in the instruction itself. This     | be provided in the instruction.With    |

| addressing mode is taking proper    | the register number present in         |

| advantage of memory address,        | instruction, operand is fetched, e.g., |

| e.g., Direct addressing mode        | Register mode                          |

| The memory address specified in     | The register contains the address of   |

| instruction may give the address    | the operand. The effective address     |

| where the effective address is      | can be derived from the content of     |

| stored in the memory. In this       | the register specified in the          |

| case effective memory address is    | instruction. The content of the        |

| present in the memory address       | register might not be the effective    |

| which is specified in the           | address. This mode takes full          |

| instruction, e.g., Indirect         | advantage of registers, e.g., Register |

| Addressing Mode                     | indirect mode                          |

| The content of base register is     | If we are having a table of data and   |

| added to the address part of the    | our program needs to access all the    |

| instruction to obtain the effective | values one by one we need              |

| address. A base register is         | something which decrements the         |

| assumed to hold a base address      | program counter/or any register        |

| and the address field of the        | which has base address. Though in      |

| instruction gives displacement      | this case register is basically        |

| MEMORY BASED<br>ADDRESSING MODES                                                                                                                                                                                                                                                                      | REGISTER BASED ADDRESSING<br>MODES                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| relative to the base address, e.g.,<br>Base Register Addressing Mode                                                                                                                                                                                                                                  | decreased, it is register based<br>addressing mode, e.g., In Auto<br>decrements mode                                                                                                                                                 |

| The content of the index register<br>is added to the address part that<br>is given in the instruction to<br>obtain the effective address.<br>Index Mode is used to access an<br>array whose elements are in<br>successive memory locations,<br>e.g., Indexed Addressing Mode                          | If we are having a table of data and<br>our program needs to access all the<br>values one by one we need<br>something which increment the<br>program counter/or any register<br>which has base address, e.g., Auto<br>increment mode |

| The content of program counter<br>is added to the address part of the<br>instruction in order to obtain the<br>effective address. The address<br>part of the instruction in this case<br>is usually a signed number which<br>can be either positive or<br>negative, e.g., Relative<br>addressing mode | Instructions generally used for<br>initializing registers to a constant<br>value is register based addressing<br>mode,and this technique is very<br>useful approach, e.g., Immediate<br>mode.                                        |

Memory based addressing modes are mostly rely on Memory address and content present at some memory location. Register based addressing modes are mostly rely on Registers and content present at some register either it is data or some memory address.

56. Define addressing modes.

Ans: Addressing Modes– The term addressing modes refers to the way in which the operand of an instruction is specified. The addressing mode specifies a rule for interpreting or modifying the address field of the instruction before the operand is actually executed.

Addressing modes for 8086 instructions are divided into two categories:

1) Addressing modes for data

2) Addressing modes for branch

The 8086 memory addressing modes provide flexible access to memory, allowing you to easily access variables, arrays, records, pointers, and other complex data types. The key to good assembly language programming is the proper use of memory addressing modes.

57. Difference between Volatile Memory and Non-Volatile Memory.

Ans:

#### **Volatile Memory:**

It is that the quite hardware that stores information quickly. it's additionally referred as temporary memory. The information within the volatile memory is hold on solely till the ability is provided to the system, once the system is turned off the information gift within the volatile memory is deleted mechanically. RAM (Random Access Memory) and Cache Memory are the common example of the volatile memory. It's quite quick and economical in nature and may be accessed apace.

#### **Non-Volatile Memory:**

It is the type of memory in which data or information remains keep within the memory albeit power is completed. ROM (Read Only Memory) is the most common example of non-volatile memory. it's not that a lot of economical and quick in nature as compare to volatile memory however stores information for the longer amount. Non-volatile memory is slow concerning accessing. All such information that must be hold on for good or for a extended amount is hold on in non-volatile memory. Non-volatile memory has a huge impact on a system's storage capacity.

Let's see that the difference between volatile and non-volatile memory:

| S.NO | VOLATILE MEMORY                                                                                                    | NON-VOLATILE MEMORY                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1.   | Volatile memory is the type of<br>memory in which data isn't keep<br>in memory as before long as<br>power is gone. | Non-volatile memory is the type of<br>memory in which data or information<br>remains keep within the memory albeit<br>power is completed. |

| 2.   | Volatile memory is not a permanent memory.                                                                         | Non-volatile memory is a permanent memory.                                                                                                |

| 3.   | It is faster than non-volatile memory.                                                                             | It is slow than volatile memory.                                                                                                          |

| 4.   | <b>RAM</b> is the example of volatile memory.                                                                      | <b>ROM</b> is the example of non-volatile memory.                                                                                         |

| 5.   | In volatile memory, data can be<br>easily transferred in comparison<br>of non-volatile memory.                     | In non-volatile memory, data can not be<br>easily transferred in comparison of<br>volatile memory.                                        |

| 6.   | Volatile memory can read and write.                                                                                | Non-volatile memory can't write, it only read.                                                                                            |

| S.NO | VOLATILE MEMORY                                                                              | NON-VOLATILE MEMORY                                                                          |

|------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 7.   | Volatile memory has less storage.                                                            | Non-volatile memory has more storage than volatile memory.                                   |

| 8.   | In volatile memory, the program's data are stored which are currently in process by the CPU. | In non-volatile memory, any kind of data<br>which has to be saved permanently are<br>stored. |

| 9.   | Volatile memory is more costly per unit size.                                                | Non-volatile memory is less costly per unit size.                                            |

| 10.  | Volatile memory has a huge<br>impact on the system's<br>performance.                         | Non-volatile memory has a huge impact<br>on a system's storage capacity.                     |

| 11.  | In volatile memory, processor has direct access to data.                                     | In non-volatile memory, processor has no direct access to data.                              |

| 12.  | Volatile memory chips are<br>generally lies on the memory<br>slot.                           | Non-volatile memory chips are contained on the motherboard.                                  |

58. Difference between Byte Addressable Memory and Word Addressable Memory.

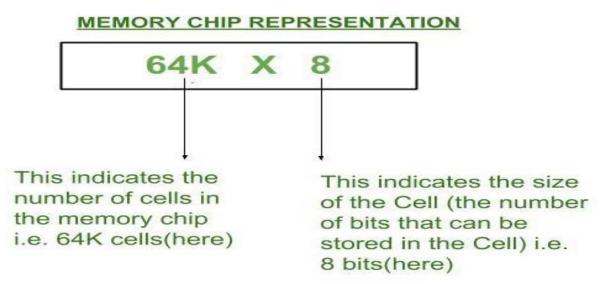

Ans: Memory is a storage component in the Computer used to store application programs. The Memory Chip is divided into equal parts called as *"CELLS"*. Each Cell is uniquely identified by a binary number called as *"ADDRESS"*. For example, the Memory Chip configuration is represented as <u>'64 K x 8'</u> as shown in the figure below.

The following information can be obtained from the memory chip representation shown above:

- **1. Data Space in the Chip =** 64K X 8

- **2. Data Space in the Cell =** 8 bits

## **3. Address Space in the Chip =** =16 bits Now we can clearly state the difference between Byte Addressable Memory & Word Addressable Memory.

| BYTE ADDRESSABLE MEMORY                                                                                                                                                          | WORD ADDRESSABLE MEMORY                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| When the <i>data space in the cell = 8 bits</i> then the corresponding <i>address space</i> is called as <u>Byte Address</u> .                                                   | When the <i>data space in the cell = word</i><br><i>length of CPU</i> then the<br>corresponding <i>address space</i> is called<br>as <u>Word Address</u> .                                                  |

| Based on this data storage i.e. <i>Bytewise storage</i> , the memory chip configuration is named as <b>Byte Addressable Memory</b> .                                             | Based on this data storage i.e. <i>Wordwise storage</i> , the memory chip configuration is named as <b>Word Addressable Memory</b> .                                                                        |

| For eg. : <b>64K X 8</b> chip has 16 bit Address<br>and <b>cell size = 8 bits (1 Byte)</b> which means<br>that in this chip, data is stored <u>byte by byte</u> .<br><b>NOTE</b> | For eg. : For a 16-bit CPU, <b>64K X 16</b> chip<br>has 16 bit Address & <b>cell size = 16 bits</b><br>( <b>Word Length of CPU</b> ) which means that<br>in this chip, data is stored <u>word by word</u> . |

i) The most important point to be noted is that in case of either of Byte Address or Word Address, *the address size* can be any number of bits (depends on the number of cells in the chip) but the *cell size* differs in each case.

ii)The default memory configuration in the Computer design is Byte Addressable .

59. What is Cache Performance and how it is calculated?

#### Ans: Cache Performance

• Average memory access time is a useful measure to evaluate the performance of a memory-hierarchy configuration.

Avg mem access time = hit time + miss rate × miss penalty

- It tells us how much penalty the memory system imposes on each access (on average).

- It can easily be converted into clock cycles for a particular CPU.

- But leaving the penalty in nanoseconds allows two systems with different clock cycles times to be compared to a single memory system.

### **Cache Performance**

- There may be different penalties for Instruction and Data accesses.

- In this case, you may have to compute them separately.

- This requires knowledge of the fraction of references that are instructions and the fraction that are data.

- The text gives 75% instruction references to 25% data references.

- We can also compute the write penalty separately from the read penalty.

- This may be necessary for two reasons:

- Miss rates are different for each situation.

- Miss penalties are different for each situation.

- Treating them as a single quantity yields a useful CPU time formula:

$\texttt{CPU time} \ = \ \texttt{IC} \times \left(\texttt{CPI}_{\texttt{execution}} + \frac{\texttt{Memory access}}{\texttt{Instruction}} \times \texttt{Miss rate} \times \texttt{Miss penalty}\right) \times \texttt{Clock Cycle Time}$

## An Example

- Compare the performance of a 64KB unified cache with a split cache with 32KB data and 16KB instruction.

- The miss penalty for either cache is 100 ns, and the CPU clock runs at 200 MHz.

- Don't forget that the cache requires an extra cycle for load and store hits on a unified cache because of the structural conflict.

- Calculate the effect on CPI rather than the average memory access time.

- Assume miss rates are as follows (Fig. 5.7 in text):

- 64K Unified cache: 1.35%

- 16K instruction cache: 0.64%

- *32K data cache: 4.82%*

- Assume a data access occurs once for every 3 instructions, on average.

#### An Example

- The solution is to figure out the penalty to CPI separately for instructions and data.

- First, we figure out the miss penalty in terms of clock cycles: 100 ns/5 ns = 20 cycles.

- For the unified cache, the per-instruction penalty is (0 + 1.35% x 20) = 0.27 cycles.

- For data accesses, which occur on about 1/3 of all instructions, the penalty is (1 + 1.35% x 20) = 1.27 cycles per access, or **0.42** cycles per instruction.

- The total penalty is **0.69 CPI**.

- In the split cache, the per-instruction penalty is (0 + 0.64% x 20) = 0.13 CPI.

- For data accesses, it is (0 + 4.82% x 20) x (1/3) = 0.32 CPI.

- The total penalty is **0.45 CPI**.

- In this case, the split cache performs better because of the lack of a stall on data accesses.

60. Define Cache Memory in Computer Organization.

Ans: **Cache Memory** is a special very high-speed memory. It is used to speed up and synchronizing with high-speed CPU. Cache memory is costlier than main memory or disk memory but economical than CPU registers. Cache memory is an extremely fast memory type that acts as a buffer between RAM and the CPU. It holds frequently requested data and instructions so that they are immediately available to the CPU when needed.

Cache memory is used to reduce the average time to access data from the Main memory. The cache is a smaller and faster memory which stores copies of the data from frequently used main memory locations. There are various different independent caches in a CPU, which store instructions and data.

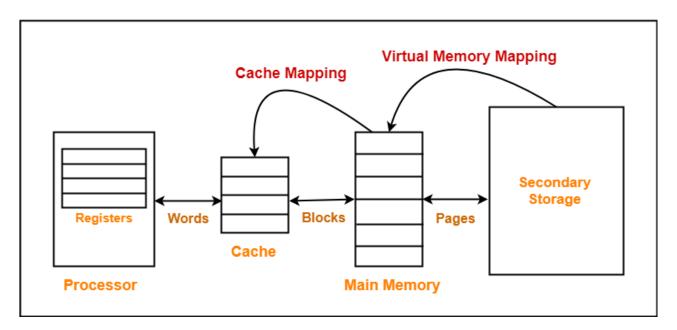

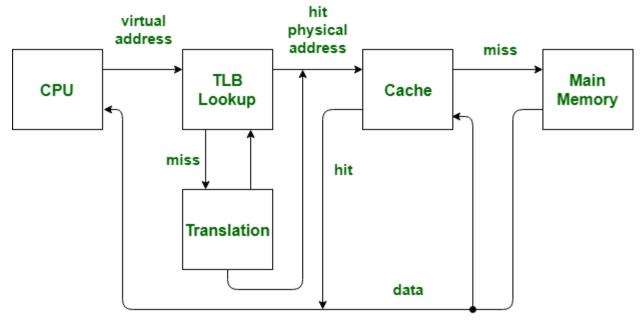

#### 61. How cache mapping is done?

Ans: When cache hit occurs,

- The required word is present in the cache memory.

- The required word is delivered to the CPU from the cache memory.

When cache miss occurs,

- The required word is not present in the cache memory.

- The page containing the required word has to be mapped from the main memory.

- This mapping is performed using cache mapping techniques.

In this article, we will discuss different cache mapping techniques.

#### **Cache Mapping-**

• Cache mapping defines how a block from the main memory is mapped to the cache memory in case of a cache miss.

#### OR

• Cache mapping is a technique by which the contents of main memory are brought into the cache memory.

The following diagram illustrates the mapping process-

Now, before proceeding further, it is important to note the following points-

## NOTES

- Main memory is divided into equal size partitions called as **blocks** or **frames**.

- Cache memory is divided into partitions having same size as that of blocks called as **lines**.

- During cache mapping, block of main memory is simply copied to the cache and the block is not actually brought from the main memory.

#### **Cache Mapping Techniques-**

Cache mapping is performed using following three different techniques-

- 1. Direct Mapping

- 2. Fully Associative Mapping

- 3. K-way Set Associative Mapping

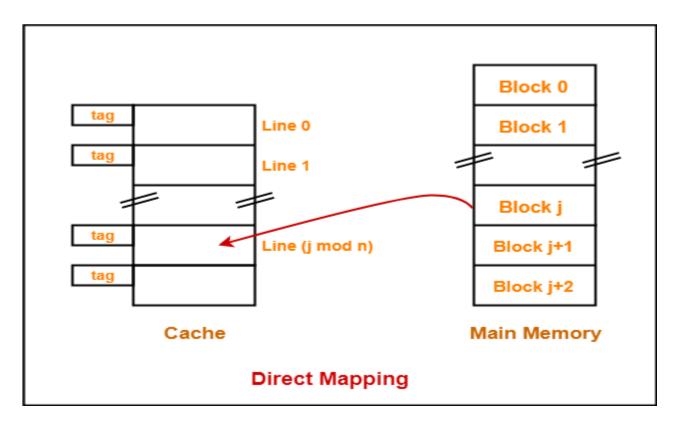

## **1. Direct Mapping-**

In direct mapping,

- A particular block of main memory can map only to a particular line of the cache.

- The line number of cache to which a particular block can map is given by-

## Cache line number

= ( Main Memory Block Address ) Modulo (Number of lines in Cache)

## Example-

- Consider cache memory is divided into 'n' number of lines.

- Then, block 'j' of main memory can map to line number (j mod n) only of the cache.

## Need of Replacement Algorithm-

In direct mapping,

- There is no need of any replacement algorithm.

- This is because a main memory block can map only to a particular line of the cache.

- Thus, the new incoming block will always replace the existing block (if any) in that particular line.

## **Division of Physical Address-**

In direct mapping, the physical address is divided as-

## Block Number

## **Division of Physical Address in Direct Mapping**

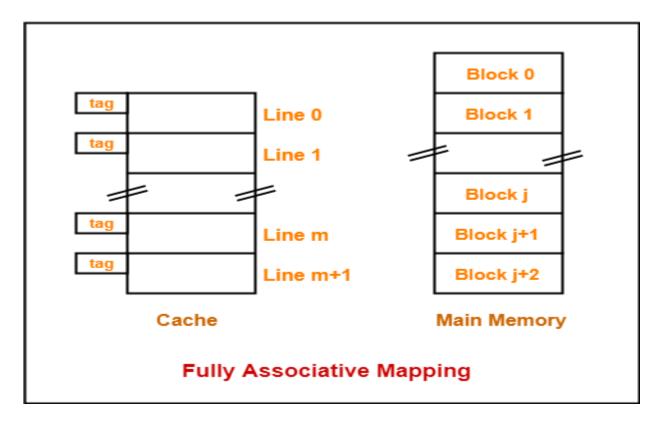

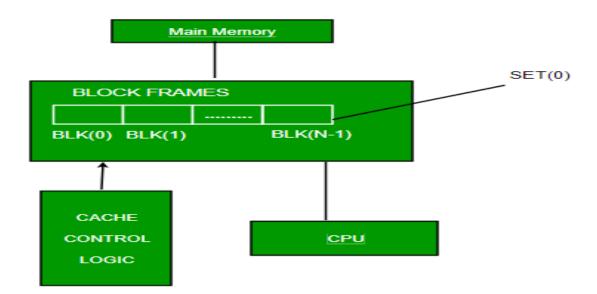

### 2. Fully Associative Mapping-

In fully associative mapping,

- A block of main memory can map to any line of the cache that is freely available at that moment.

- This makes fully associative mapping more flexible than direct mapping.

#### Example-

Consider the following scenario-

Here,

- All the lines of cache are freely available.

- Thus, any block of main memory can map to any line of the cache.

- Had all the cache lines been occupied, then one of the existing blocks will have to be replaced.

## Need of Replacement Algorithm-

In fully associative mapping,

- A replacement algorithm is required.

- Replacement algorithm suggests the block to be replaced if all the cache lines are occupied.

- Thus, replacement algorithm like FCFS Algorithm, LRU Algorithm etc is employed.

#### **Division of Physical Address-**

In fully associative mapping, the physical address is divided as-

Block Number / Tag Block / Line Offset

# **Division of Physical Address in Fully Associative Mapping**

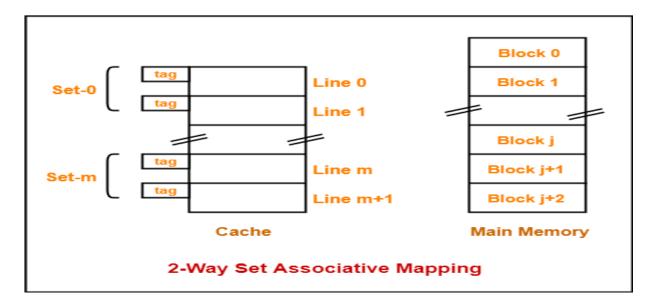

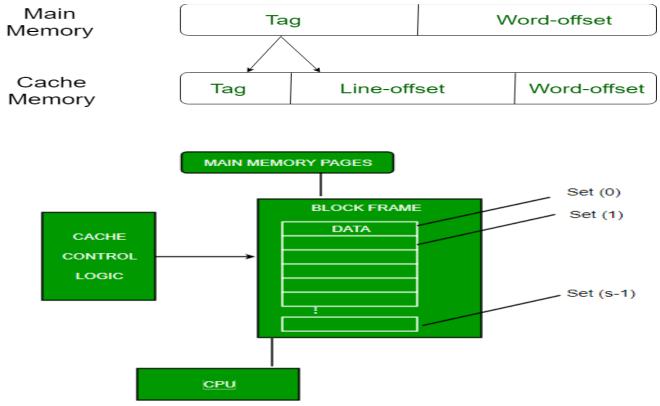

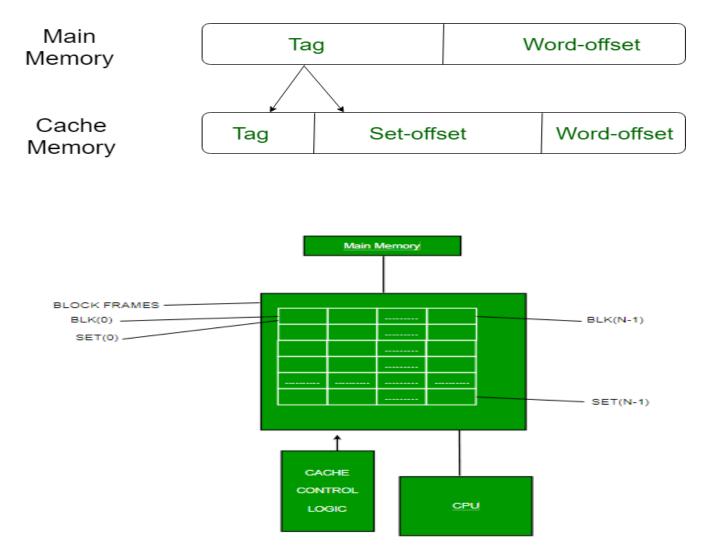

#### 3. K-way Set Associative Mapping-

In k-way set associative mapping,

- Cache lines are grouped into sets where each set contains k number of lines.

- A particular block of main memory can map to only one particular set of the cache.

- However, within that set, the memory block can map any cache line that is freely available.

- The set of the cache to which a particular block of the main memory can map is given by-

# Cache set number = ( Main Memory Block Address ) Modulo (Number of sets in Cache)

#### Example-

Consider the following example of 2-way set associative mapping-

Here,

- k = 2 suggests that each set contains two cache lines.

- Since cache contains 6 lines, so number of sets in the cache = 6/2 = 3 sets.

- Block 'j' of main memory can map to set number (j mod 3) only of the cache.

- Within that set, block 'j' can map to any cache line that is freely available at that moment.

- If all the cache lines are occupied, then one of the existing blocks will have to be replaced.

62. Difference between Contiguous and Non-contiguous Memory Allocation

#### Ans:

#### 1. Contiguous Memory Allocation :

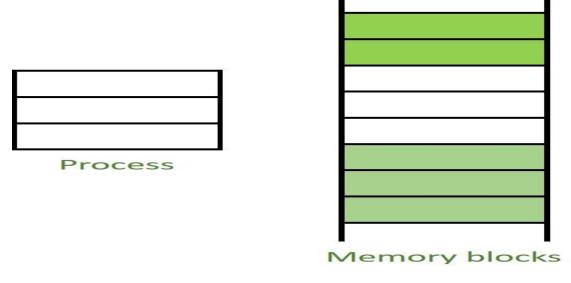

Contiguous memory allocation is basically a method in which a single contiguous section/part of memory is allocated to a process or file needing it. Because of this all the available memory space resides at the same place together, which means that the freely/unused available memory partitions are not distributed in a random fashion here and there across the whole memory space.

#### **Contiguous Memory Allocation**

The main memory is a combination of two main portions- one for the operating system and other for the user program. We can implement/achieve contiguous memory allocation by dividing the memory partitions into fixed size partitions.

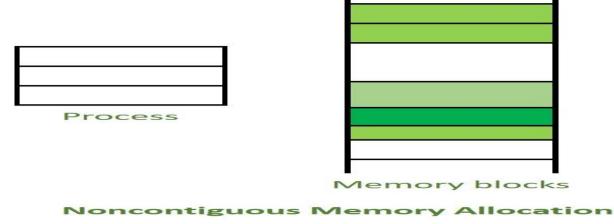

#### 3. Non-Contiguous Memory Allocation :

Non-Contiguous memory allocation is basically a method on the contrary to contiguous allocation

method, allocates the memory space present in different locations to the process as per it's

requirements. As all the available memory space is in a distributed pattern so the freely available memory space is also scattered here and there.

This technique of memory allocation helps to reduce the wastage of memory, which eventually gives rise to Internal and external fragmentation.

| S.NO. | CONTIGUOUS<br>MEMORY<br>ALLOCATION                                                                 | NON-CONTIGUOUS<br>MEMORY ALLOCATION                                                              |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1.    | Contiguous memory<br>allocation allocates<br>consecutive blocks of<br>memory to a file/process.    | Non-Contiguous memory<br>allocation allocates separate<br>blocks of memory to a<br>file/process. |  |  |  |  |  |

| 2.    | Faster in Execution.                                                                               | Slower in Execution.                                                                             |  |  |  |  |  |

| 3.    | It is easier for the OS to control.                                                                | It is difficult for the OS to control.                                                           |  |  |  |  |  |

| 4.    | Overhead is minimum as<br>not much address<br>translations are there<br>while executing a process. | More Overheads are there as<br>there are more address<br>translations.                           |  |  |  |  |  |

| 5.    | Internal fragmentation<br>occurs in Contiguous<br>memory allocation<br>method.                     | External fragmentation occurs in<br>Non-Contiguous memory<br>allocation method.                  |  |  |  |  |  |